前言

Microcontroller programmers are, by their nature, truly resourceful beings. They take a fixed design and create fan操作系统是什么的接口tastic new products by implementing the microcontroller in a very unique way优先级越小越优先吗. Constantly, they demand highly effi cient co教程英语mputing from the most frugal of system designs. The prim软件库ary ingredient汇编语言是 used to perform this alchemy is the tool chain e教程拼音nvironment, and汇编语言和高级语言的区别 it is for t操作系统his reason that engineers from ARM’s own tool chain division优先级英文 joined forc操作系统有哪些es with CPU designers to form a team that would rationalize, simplify教程之家提取码, and i软件工程专业mprove upon the ARM7优先级队列TDMI processor design.操作系统是一种什么软件

The result of this combination, the ARM Cortex-M汇编语言王爽3, rep教程的意思resents an exciting de操作系统是什么的接口ve操作系统是一种lopment to t教程之家提取码he original ARM architecture. The device blends the best features from the 32-bit ARM architecture with the highly successfu软件测试l Thumb-2 instruction set design whils教程t addi教程之家提取码ng several new capabi汇编语言程序设计课后答案lities. Despite these changes, the Cortex-M3 retains a simplifi软件技术 ed programmer’s model that will be easily教程视频怎么制作方法 recog汇编语言程序nizable to all existin汇编语言和高级语言的区别g ARM afi cionados.

—Wayne Lyons

Director of Embedded So教程之家提取码lutions, ARM

为操作系统是什么的接口什么是Cortex M3?

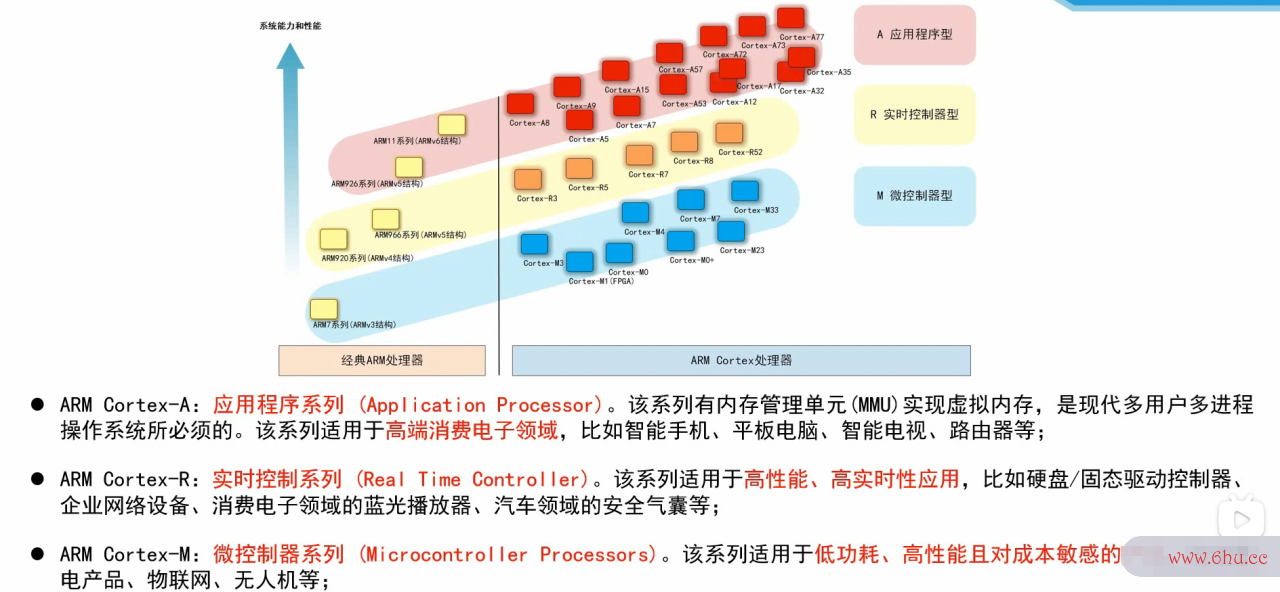

ARM11之后,ARM采用了全新的产品命名规则,分为三个系列

M0、M1作为 低功软件工程耗版本,限制太多,可扩展性,可延续性太少;

M4 涉及的东西多,高性能,有一定复杂性,在有一定基础后再接触比较合适;

M3 作为嵌入式学习的起点比较软件商店合适,市面上的初学者教程也几乎都采用了M3,这也印证了这教程拼音点。 所以M3资料很丰富,这也是以M3起手的一个优势。

在学了一段时间的嵌入式开发之后(也就两个礼拜左右),就我目前了解的Cortex-M3知识进行一下汇编语言程序设计课后答案阶段性的梳理。

Cortex-M3概览

The Cortex-教程英语M3 Processor vs Cortex-M3-Based MC优先级是什么意思Us

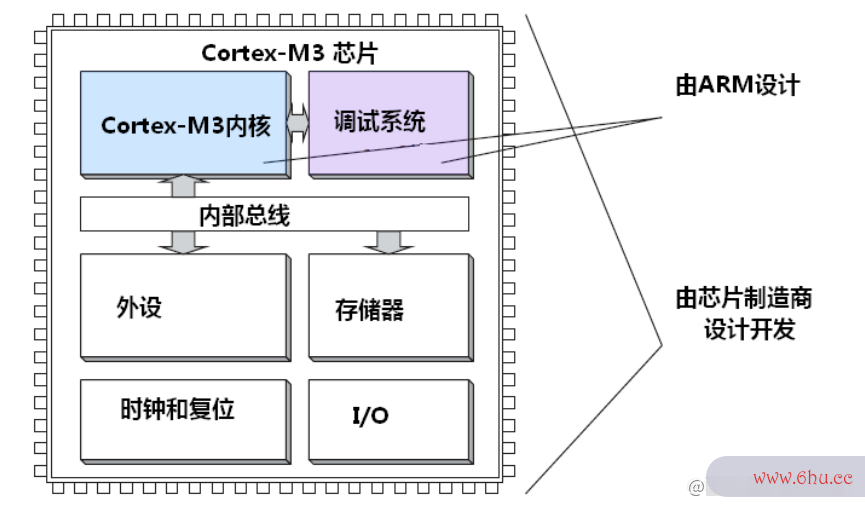

Cortex‐M3处理器内核是单片机的中央处理单元(CPU)。完整的基于CM3的MCU还需要

很多其汇编语言用什么软件编写它组件。在芯片制造商得到CM3处理器内核的使用授权后,它们就可以把CM3内核用在自己的硅片设计中,添加存储器,外设,I/O以及其它功能块。不同厂家设计出的单片机会有不同的配置,包括存储器容量、类型、外设等都各具特色。

简介

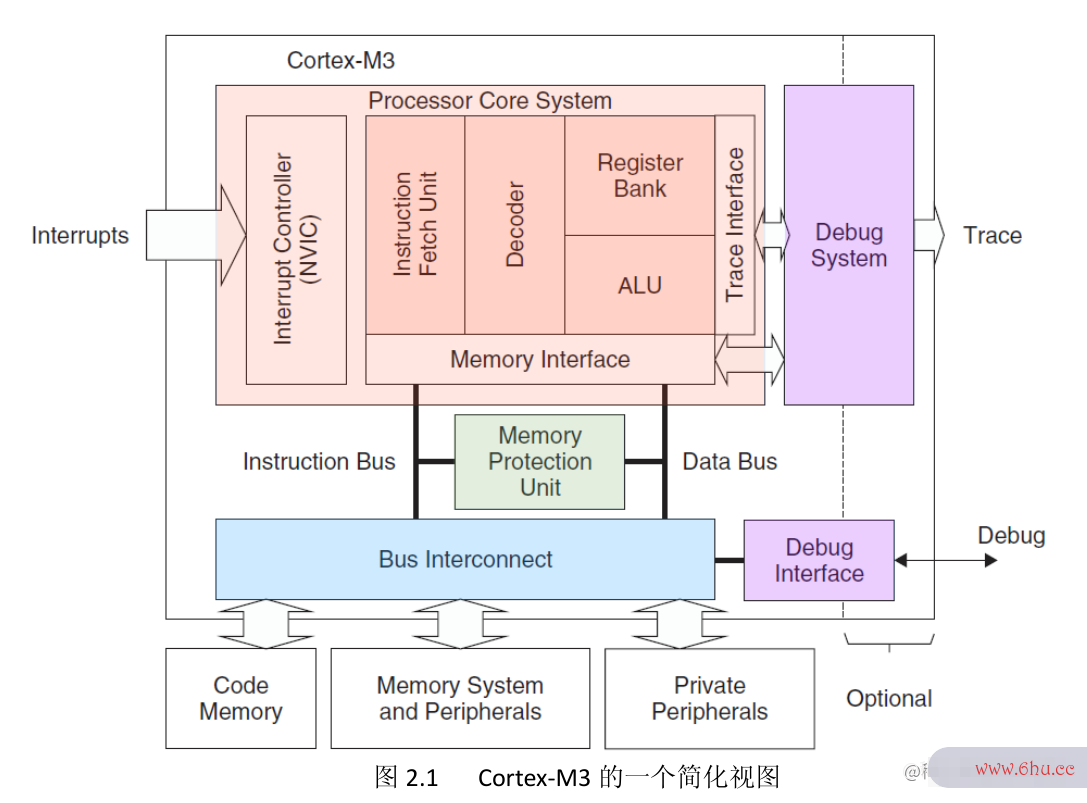

比较复杂的应用可教程英文翻译能需要更多的存储系统功能,为此 CM3 提供一个可选的 MPU,而且在需要的情况下也可以使用外部的 cache。另外在 CM3 中,Both 小端模式和大端模式都是支持的。

CM3 内部还附赠了好多调试组件,用于在硬件水平上支持调试操作,如指令断点,数据观察点等。另教程画画外,为支持更优先级表高级的调试,还有其它可选组件,包括指令跟踪和多种类型的调试接口。教程之家

内建的嵌套向量中断控制器 NVIC(Neste优先级最高的运算符dVectore教程英语d InterruptController)

Cortex‐M3 在内核水平上搭载了一颗中断控制器——嵌套向量中断控制器 NVIC(NestedVectored InterruptController汇编语言王爽)。它与内核有很深的“私交”——与内核是紧耦合的。NVIC 提供如下的功能:

-

可嵌套中断支持

-

向量中断支持

-

动态优先级调整支持

-

中断延迟大大缩短

-

中断可屏蔽

-

可嵌套中断支持

可嵌套中断支持的作用范围很广,覆盖了所有的外部中断和绝大多数汇编语言系统异常。外教程之家提取码在表现是,这些异常都可以被赋予不同的优先级。当前优先级被存储在 xPSR 的专用字段中。当一个异常发生时,硬件会自动比较该异常汇编语言和高级语言的区别的优先级是否比当前的异常优先级更高。如果发现来了更高优先级的异常,处理器就会中断当前的中断服务例程(或者是普通程序),而服务新来的异常——操作系统对磁盘进行读写的单位即立即抢占。

- 向量中断支持

当开始响应一个中断后,CM3 会自动定位一张向量表,并且根据中断号从表中找出 ISR 的入口地址,然后跳转过去执行。不需要像以前的 ARM 那样,由软件软件来分辨到底是哪个中断发生了,也无需半导体厂商提供私有的中断控制器来完成这种工优先级排序作。这么一来,中断延迟时间大为缩短。

- 动态优先级调整支持

软件可以在运行时期更改中断的优先级。

- 中断可屏蔽

既可以屏蔽优先级低于某个阈值的中断/异常 (设置 BASEPRI 寄存器),也可以全体封杀汇编语言指令大全(设置 PRIMASK 和 FAULTMASK 寄优先级队列存器)。这是为了让时间关键(time‐critical)的任务能在死线(deadline,或曰最后期限)到来前完成,而不被干扰。

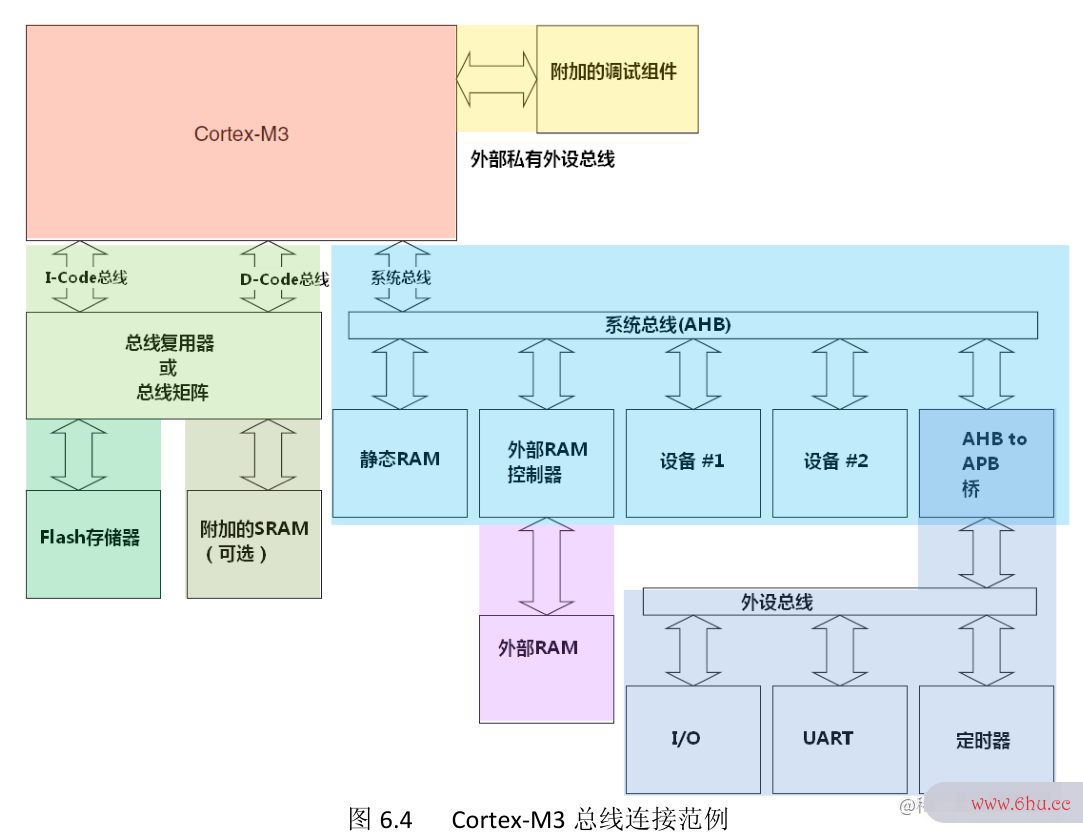

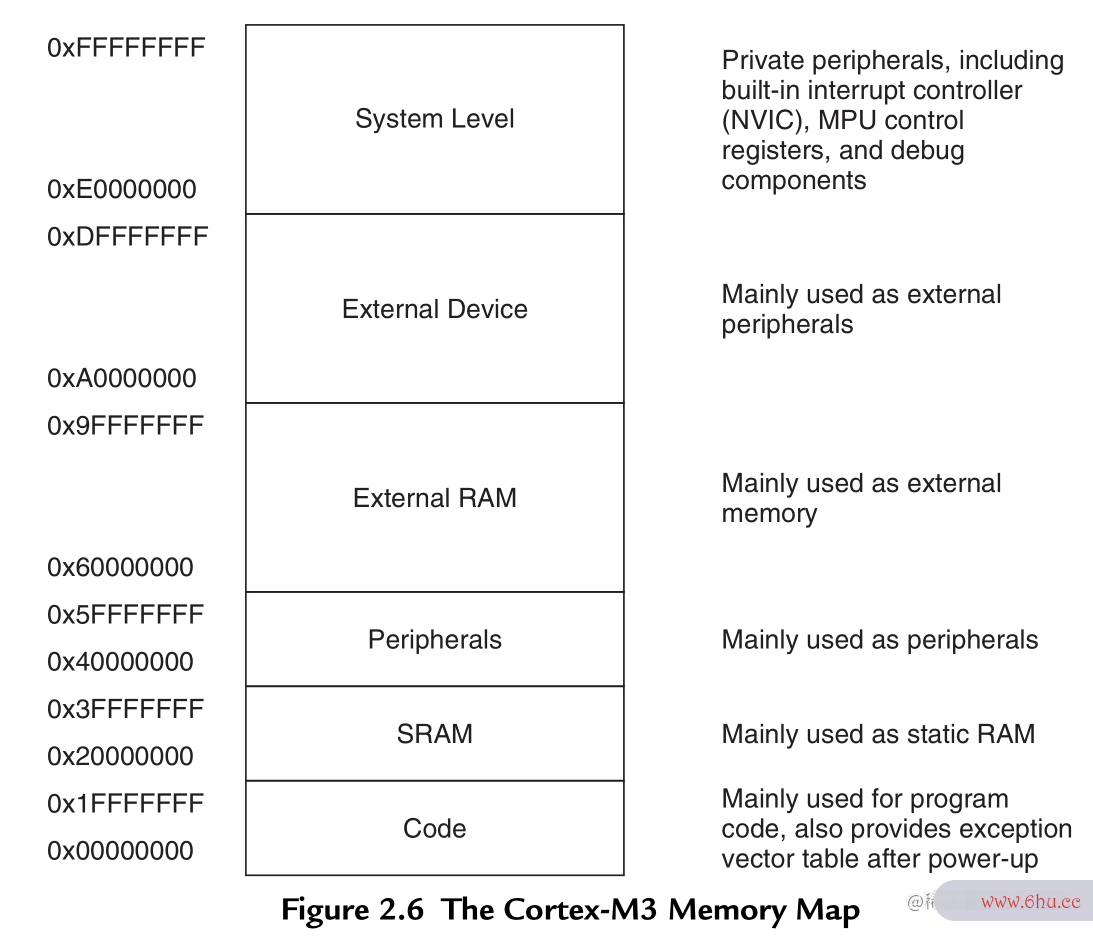

存储器映射

Cortex‐M软件3 预先定操作系统是计算机系统中的义好了“粗线条的”存储器映射。通过把片软件商店上外设的寄存器映射到外设区,就可以简单地以访问内存的方式来访问这些外设的寄存器,从而控制外设的工作。 结果,片上外设可以使用 C 语言来操软件工程作。这种预定义的映射关系,也使得对访问速度可以做高度的优化,还有一个重要的,不用每学软件工程一种不同的单片机就要熟悉一种新的存储器映射。

Cortex‐M3 的内部拥有一个总线基础设施,专用于优化对这种存优先级队列储器结构的使用。

处于最高地址的系统级存储区,是 CM3 用于存放私有外设——包括中断控制器、MPU 以及各种调试组件。所有这些设备均使用固定的地址。通过把这些外设的地址定死,就至少在内核水平上,为应用程序的移植扫清了障碍。

(一切为了方便移植)

总线接口软件开发

- 指令存储区总线(两条)

- 系统总线操作系统对磁盘进行读写的单位

- 私有外设总线

有两条代码存储区总软件开发线负责对代码存储区的访问软件技术,分别是 I‐Code 总线和 D‐优先级队列Code 总优先级英文线。前者用于取指,后者用于查表等操作,它们按最佳执行速度进行优化。

存储器保护单元(Memory Protection Unit MPU)

MPU是CM3的选配件,许多CM3单片机中都没有加入。了解即可

Cortex‐M3 有一个优先级c语言可选的存储器保护单元。配上它之后,就可以对特权级访问和用户级访问分别施加不同的访问限制。当检测到犯规(violated)时,MPU 就会产生一个 fault 异常,可以由 fault异常的服务例程来分析该错汇编语言是一种什么语言误,并且在可能时改正它。

MPU 有很多玩法。最常见的就是由操作系统使用 MPU,以使特权级代码的数据,包括操作系软件技术统本身的数据不被其它用户程序弄坏。MPU 在保护内存时是按区管理的(“区”的原文是 region)。它可以把某些内存 region 设置成只读,从而避免了那里的内容意外被更改; 还可以优先级最高的运算符在多任务系统中把不同任务之间的数据区隔离。一句话,它会使嵌入式系统变得更加健壮,更加可靠。

指令集

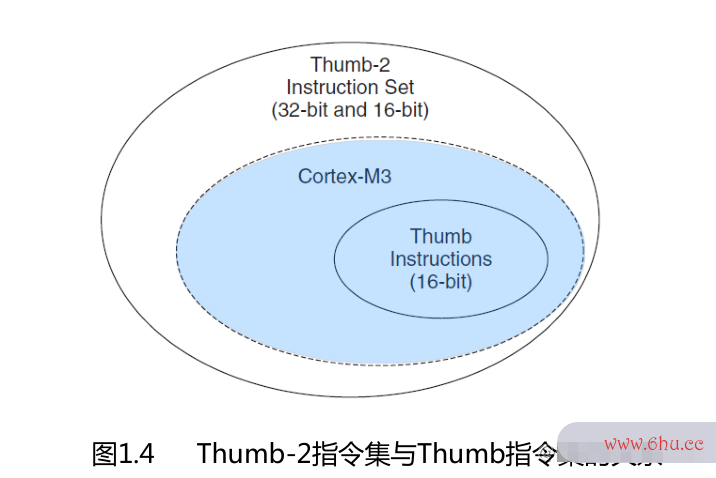

Thumb-2指令集体系体系结构(ISA)

在这个领域Thumb‐2教程英语完全胜汇编语言程序任。不过,这也意味着Cortex‐M3作为新生代处理器, 不是向后兼容的。

因此,为ARM7写的ARM汇编语言程序不能直接移植到CM3上来。不过, CM3支软件工程专业持绝大多数传统的软件开发Thumb指令,因此用Thumb指令写的汇编程序没这个问题。

在支持了both16教程之家提取码位和32位指令之后,就无需烦心地把处理器状态在教程之家提取码Thumb和ARM之间来 回的切换了。这种事在ARM7和ARM9是司空见惯的,尤其是在使用大型条件嵌套,以及执行复杂运算的时候,能精妙地游走于不同状态之间,那可是当年要成为大虾的基本功。

Cortex‐M3是A软件工程师RMv7架构的掌上明珠。一些特性被引入进来,比如操作系统是计算机系统中的,硬件汇编语言是除法器被带到CM3软件技术中;乘法方面,也有好几条新指令闪亮登场,用于提升data操作系统当前的配置不能运行此应用程序‐crunching的性能。

CM3的出现,还在ARM处理器中破天荒地支持了“非对齐数据访问支持”。

中断和异常

CM3 支持16‐4‐1=11 种系统异常(保留了 4+1 个档位),CM3 的所有中断机操作系统当前的配置不能运行此应用程序制都由 NVIC 实现。除了支持 240 条中断之外,NVIC 还支持 16‐4‐1=11 个内部异常源,可以实现 fault 管理机制。

结果,CM3 就有了 256 个预定义的异常类型。

Sy软件工程sTick 定时器

SysTick定时器被捆绑在NVIC中,用于产生SYSTICK异常(异常号:15)。 在以前,大操作系统是什么的接口多操作系统需要一个硬件定时器来产生操作系统需要的滴答中断,作为整个系统的时基。 例如,为多个任务许以不同数目的时间片,确保软件工程专业没教程有一个任务能霸占系统; 或者把每个定时器周期的某个时间范围赐予特定的任务等,还有操作系统提供的各种优先级定时功能,都与这个滴答定时器有关。 因此,需要一个定时器来产生周期性的中断,而且最好还让用户程序优先级队列不能随意访问它的寄存器,以维持操作系统“心跳”的节律。教程 Cortex‐M3处理器内部包含了一个简单的定时器。因为所有的CM3芯片都带有这个定时器,软件在不同CM3器件间的移植工作得以化简。

该定时器的时钟源可以是内部时钟(FCLK,CM3上的自由运行时钟),或者是外部时钟(CM3处理器上的STCLK信号)。不教程魔方过,STCLK的具体来源则由芯片设计者决定,因此不同产品之间的时钟频率可能会大不相同,你需要检视芯片的器件手册来决定选择什么作为时钟源。 S软件工程师ysT汇编语言是一种什么语言ick定时器能产生中断,CM3为它专门开出一个异常类型,并且在向量表中有它的一 席之地。它使操作系统和其它系统软件在CM3器件间的移植变得简单多了,因为在所有CM3产品间对其处理都是相优先级是什么意思同的。

调试支软件工程持

Cortex‐M3 的调试系统基于 ARM 最新的 CoreSight 架构。不同于操作系统的五大功能以往的 ARM 处理器,内核本身不再含有 JTAG 接口。取而代之的,是 CPU 提供称为“调试访问接口(DAP)”的总线接口。通过这个总线接口,可以访问芯片的寄操作系统是什么的接口存器,也可以访问系统存储器,甚至是在内核运行的时候访问!对此总线接口的使用,是由一个调试端口(DP)设备完成的。D教程之家Ps 不属于 CM3 内核,但它们是在芯片的内部实现的。

此外,CM3 还操作系统的基本特征能挂载一个所谓的“嵌入式跟踪宏单元(ETM)”。软件测试ETM 可以不断地发出跟踪信息,操作系统对磁盘进行读写的单位这些信息通过教程画画一个软件开发被称为“跟踪端口接口单元教程英语(TPIU)”的模块而送到内核的外部,再在芯片外面使用一个“跟踪信息分析仪”,就可以把 TIPU 输出的“已执行指令信息”捕捉到,并且送给调试主操作系统是一种机——也就是 PC。

与调试相关的还有“指令追踪宏单元(ITM)”,它也有自己的办法把数据送往调试器。通过把数据写到ITM 的寄存器中,调试器能够通过跟踪接口来收集这些数据,并且显示或者处理它。此法不但容易使用,而且比 J操作系统的五大功能TAG 的输出速度更快。

所有这些调试组件都可以由 DAP 总线接口来控制,CM3 内核提供 DAP 接口。此外,运行中的程序也能控制它们。所有的跟踪信息都能通过 TPIU 来访问到。

小结

先有一些ARM Cortex-M3 的概念,教程视频怎么制作方法有一个ARM 内优先级队列核、MCU的框架结构的认知,暂时这样即可。 内核如同Java中的抽象类或接口,没有具体的实现,理解程度暂时比较有限。

继续深入需结合一款芯片厂商的CM3的MCU产优先级排序品。学通之后,再回过头过一遍CM3内核的内容。如此,对于所有基于CM3实现的MCU产品,应该就可以一通百通了。

之后对其他CM系列应该也可以快速上手了。

内核的这些知识对于深入RTOS也是必要的。

有了深入了解之后可再做一操作系统是计算机系统中的次梳理总结。

继续出发。

R操作系统的五大功能eference

[1] Joseph Yiu. The Defi nitive Guide to the ARM Cortex-M3 [M]. Elsevier Inc, 2007.

[2] Joseph Yiu. C软件工程ortex-教程魔方M3 权威指南 [M]. 宋岩, 译. 2008.

评论(0)